Sudip S. Dosanjh Sandia National Laboratories Albuquerque, NM Jeffrey A. Nichols Oak Ridge National Laboratory Oak Ridge, TN

SAND2008-2204P

Sandia is a Multiprogram Laboratory Operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy Under Contract DE-ACO4-94AL85000.

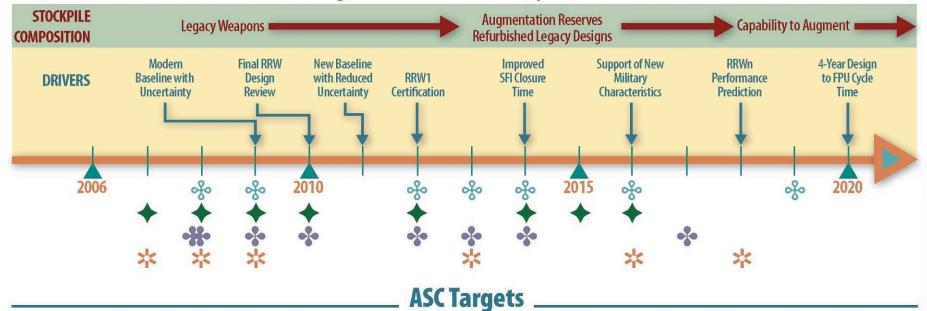

#### **Computational Weapons Science and Simulation:**

Targets to address Nuclear Weapons Issues

#### FOCUS AREA 1: ADDRESS NATIONAL

- SECURITY SIMULATION NEEDS

- \* 2008: National code strategy

- 2009: Modular physics and engineering packages for national weapons codes

- 2012: Tested capability to address emerging threats, effects, and attribution

- 2013: 50% improvement in setup-to-solution time for SFI simulations (with respect to 2006)

- 2014: Full-system engineering and physics simulation capability

2016: Capability to certify fire safety for an unfielded weapon 2019: 50% improvement in setup-to-solution time for SFI simulations (with respect to 2013)

#### FOCUS AREA 2: ESTABLISH A VALIDATED PREDICTIVE CAPABILITY FOR KEY PHYSICAL PHENOMENA

- + 2007: Launch Thermonu dear Burn Initiative (TBI) collaboration

- + 2008: Realistic plutonium aging simulations

- ✤ 2009: Science-based replacement for Knob #1

- ◆ 2010: Science-based models for neutron tube simulations

- ✤ 2012: Validated science-based replacement for Knob #2

- 2014: NIF-validated simulations supporting replacement of knob #3

- 2015: Science-based models for fire excitation simulations

2016: Predictive model for Knob #4

#### FOCUS AREA 3: QUANTIFY AND AGGREGATE UNCERTAINTIES IN SIMULATION TOOLS

- \* 2008: National verification & validation strategy

- \* 2008: Assessment of major simulation uncertainties

- \* 2009: Shared weapons physical databases

- 🍫 2010: Uncertainty Quantification (UQ) methodology for QMU

- \* 2012: 20% reduction in overall prediction error bars (with respect to 2006)

- 2013: Re-assessment of major simulation uncertainties

- \* 2014: Demonstrated uncertainty aggregation for QMU

- \* 2017: 20% Reduction in overall prediction error bars (with respect to 2012)

#### FOCUS AREA 4 : PROVIDE MISSION-RESPONSIVE COMPUTATIONAL ENVIRONMENTS

\*2007: Initiate new National User Facility model for capability supercomputing

- 2008: Seamless user environments for capacity computing

- \*2009: Petascale computing

- \*2013: Seamless user environments for capability computing \*2016: 100x petascale computing \*2018: Exascale computing

- 20 16: Exascale computing

### **Software Trends**

### Science is getting harder to solve on Leadership systems

### **Application trends**

- Scaling limitations of present algorithms

- More complex multi-physics requires large memory per node

- Need for automated fault tolerance, performance analysis, and verification

- Software strategies to mitigate high memory latencies

- Hierarchical algorithms to deal with BW across the memory hierarchy

- Innovative algorithms for multi-core, heterogeneous nodes

- Model coupling for more realistic physical processes

### **Emerging Applications**

- Growing importance of data intensive applications

- Mining of experimental and simulation data

### **Industry Trends**

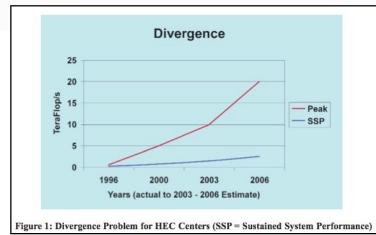

#### Existing industry trends not going to meet HPC application needs

- Semi-conductor industry trends

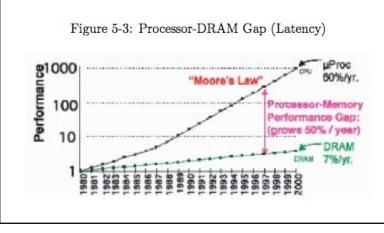

- Moore's Law still holds, but clock speed now constrained by power and cooling limits

- Processors are shifting to multi/many core with attendant parallelism

- Compute nodes with added hardware accelerators are introducing additional complexity of heterogeneous architectures

- Processor cost is increasingly driven by pins and packaging, which means the memory wall is growing in proportion to the number of cores on a processor socket

- Development of large-scale Leadership-class supercomputers from commodity computer components requires collaboration

- Supercomputer architectures must be designed with an understanding of the applications they are intended to run

- Harder to integrate commodity components into a large scale massively parallel supercomputer architecture that performs well on full scale real applications

- Leadership-class supercomputers cannot be built from only commodity components

### Moore's Law + Multicore → Rapid Growth in Computing Power

2007 - 1 TeraFLOPs on a chip • 275 mm<sup>2</sup> (size of a dime) & 62 W

1997 - 1 TeraFLOPs in a room • 2,500 ft<sup>2</sup> & 500,000 W

# The Memory Wall significantly impacts the performance of our applications

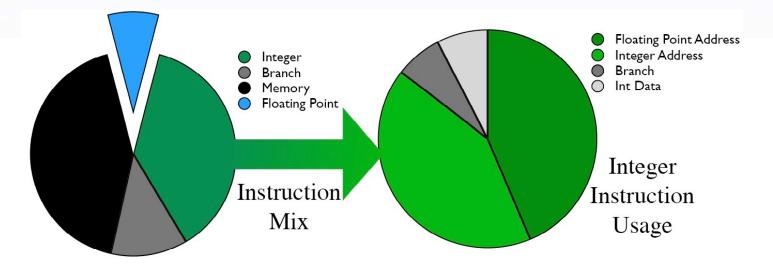

- Most of DOE's Applications (e.g., climate, fusion, shock physics, ...) spend most of their instructions accessing memory or doing integer computations, not floating point

- Additionally, most integer computations are computing memory Addresses

- Advanced development efforts are focused on accelerating memory subsystem performance for both scientific and informatics applications

### The Need for HPC Innovation and Investment is Well Documented

Report of the High-End Computing Revitalization Task Force (HECRTF), May 2004

"Requirements for ASCI", Jasons Report, Sept 2002

## National Research Council, "Getting Up To Speed The Future of Supercomputing", Committee on the Future of Supercomputing, 2004

"Recommendation 1. To get the maximum leverage from the national effort, the government agencies that are the major users of supercomputing should be jointly responsible for the strength and continued evolution of the supercomputing infrastructure in the United States, from basic research to suppliers and deployed platforms. The Congress should provide adequate and sustained funding."

### Impediments to Useful Exascale Computing

- Data Movement

- Local

- cache architectures

- main memory architectures

- Remote

- Topology

- Link BW

- Injection MW

- Messaging Rate

- File I/O

- Network Architectures

- Parallel File Systems

- Disk BW

- Disk latency

- Meta-data services

- Power Consumption

- Do Nothing: 100 to 140 MW

- Scalability

- 10,000,000 nodes

- 1,000,000,000 cores

- 10,000,000,000 threads

- Resilience

- Perhaps a harder problem than all the others

- Do Nothing: an MTBI of 10's of minutes

- Programming Environment

- Data movement will drive new paradigms

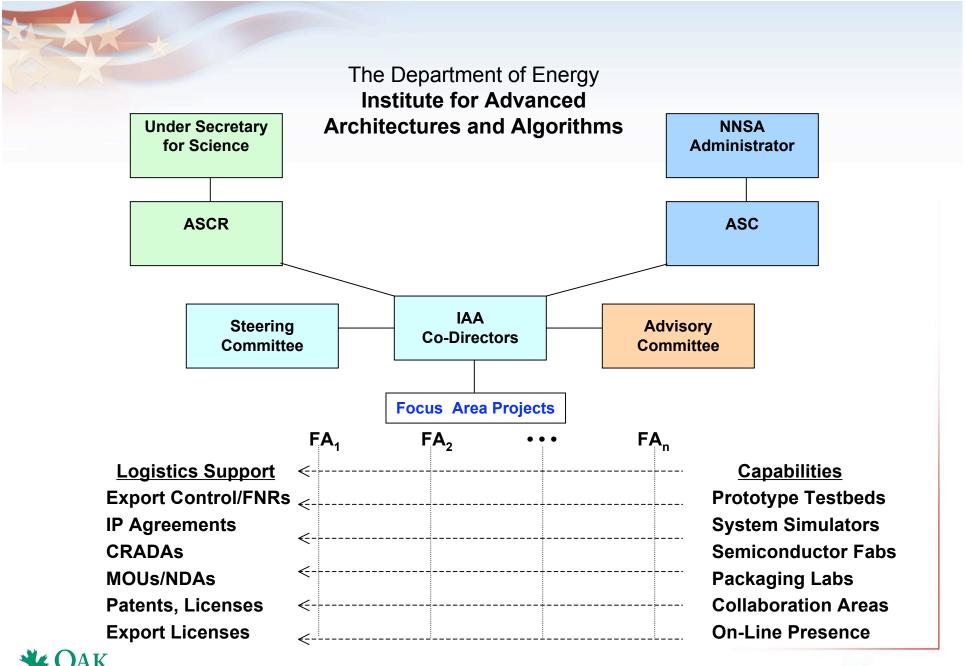

## **IAA Mission and Strategy**

IAA is proposed as the catalyst for co-design and development of architectures and algorithms/applications to create synergy in their respective evolutions

- Focused R&D on key impediments to high performance in partnership with industry and academia

- Foster the integrated co-design of architectures and algorithms to enable more efficient and timely solutions to mission critical problems

- Partner with other agencies (e.g., DARPA, NSA ...) to leverage our R&D and broaden our impact

- Impact vendor roadmaps by committing National Lab staff and funding the Non-Recurring Engineering (NRE) costs of promising technology development and thus lower risks associated with its adoption

- Train future generations of computer engineers, computer scientists, and computational scientists, thus enhancing American competitiveness

- Deploy prototypes to prove the technologies that allow application developers to explore these architectures and to foster greater algorithmic richness

### Uniqueness

- Partnerships with industry, as opposed to contract management

- Cuts across DOE and other government agencies and laboratories

- A focus on impacting commercial product lines

- National competitiveness

- Impact on a broad spectrum of platform acquisitions

- A focus on problems of interest to DOE

- National Security

- Science

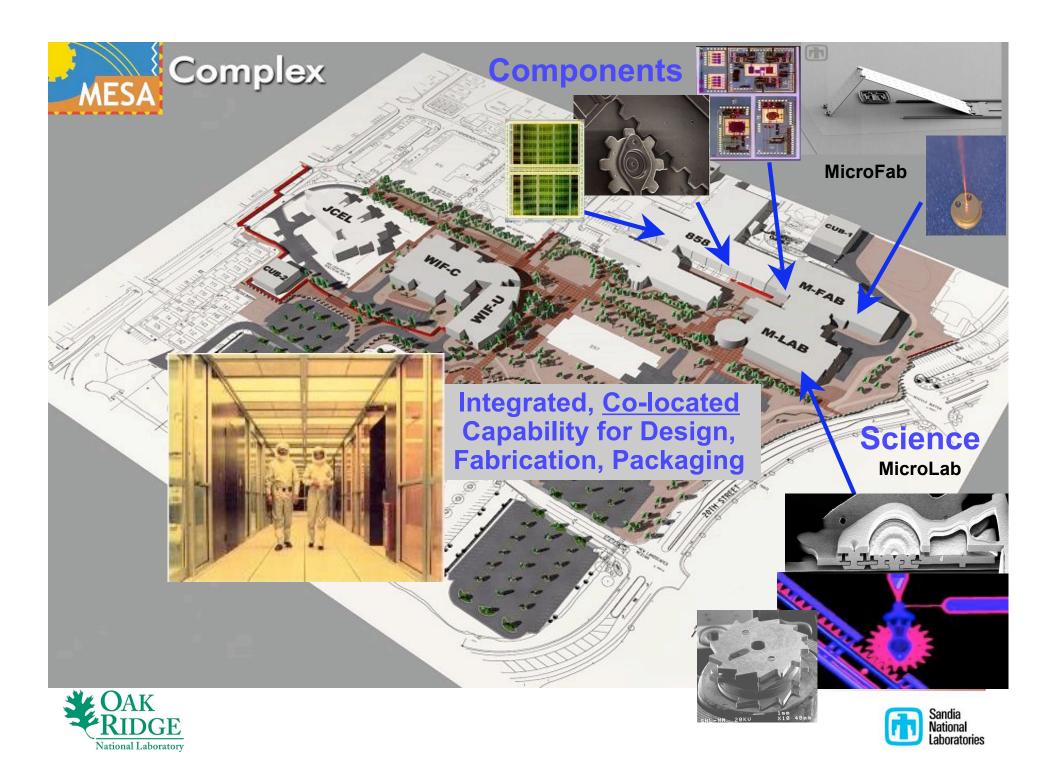

- Sandia and Oak Ridge have unique capabilities across a broad and deep range of disciplines

- Applications

- Algorithms

- System performance modeling and simulation

- Application performance modeling

- System software

- Computer architectures

- Microelectronics Fab, Packaging Lab, ...

### **Execution Plan**

- Project Planning

- Joint SNL/ORNL meetings

- Workshops

- Work with industry and academia to define thrust areas

- "Memory Opportunities for High-Performance Computing", Jan 2008 in Albuquerque (Fred Johnson and Bob Meisner were on the program committee)

- Planning started for an Interconnect Workshop, Summer 2008

- Planning started for an Algorithm Workshop, Fall 2008

- Training

- Fellowships, summer internships, and interactions with academia to help train the next generation of HPC experts.

- Define and prioritize focus areas

- High-speed interconnects \*

- Memory subsystems \*

- Power

- Processor microarchitecture

- RAS/Resiliency

- System Software

- Scalable I/O

- Hierarchical algorithms \*

- System simulators \*

- Application performance modeling

- Programming models

- Tools

- \* FY '08 Project Starts

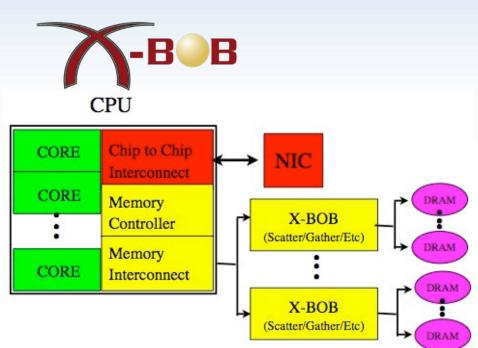

### **Memory Project**

**Vision**: Create a **commodity** memory part with support for HPC data movement operations.

**Approach**: new high-speed memory signaling technology inserts an ASIC (the Buffer-on-Board, or BOB) between the CPU and memory. Add data movement support in the ASIC.

#### Near Term Goals:

- Define in-memory operations (scatter/gather, atomic memory operations, etc.)

- Define CPU/X-BOB coherency

#### Long Term Goals:

• Create a commodity memory part that increases effective bandwidth utilization

#### **Potential Partners:**

- Industry: Micron (since June 05), AMD, SUN, Intel, Cray, IBM

- Academia: USC/ISI (Draper/Hall), LSU (Sterling)

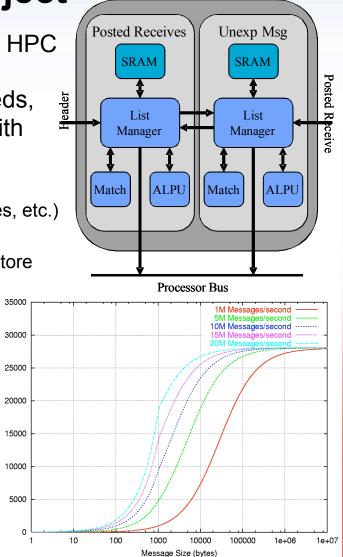

### **Interconnect Project**

**Vision**: Ensure next generation interconnects satisfy HPC needs

**Approach**: Provide understanding of application needs, explore designs with simulation, prototype features with vendors

#### Long Term Goals:

- Scalability: >100,000 ports (including power, cabling, cost, failures, etc.)

- High Bandwidth: 1TF sockets will require >100GBps

- High Message Throughput: >100M for MPI; >1000M for load/store

- *Low Latency*: Maintain ~1us latency across system

- *High Reliability*: <10<sup>-23</sup> unrecovered bit error rate

#### Near Term Goals:

- · Identify interconnect simulation strategy

- Characterize interconnect requirements on mission apps <sup>®</sup>

- Develop MPI models & tracing methods

- Pursue small collaboration project with industry partner

#### **Potential Collaborators:**

- Academic: S. Yalamanchili (parallel simulation), B. Dally (topologies, routing), K. Bergman (optics)

- Industry: Intel, Cray

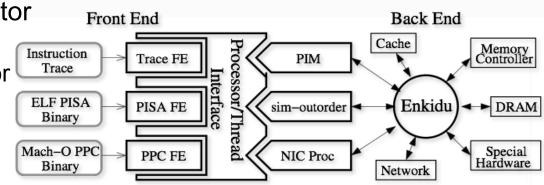

### **Simulator Project**

#### Long Term Vision: Become the HPC community standard simulator Long Term Goals

- Highly scalable parallel simulator

- Multi-scale simulation

- Technology model interface

### Near Term-Goals

- Prototype parallel simulator

- x86 Front-/Back-end models

- Integrate MPI Models

- Tracing for Interconnect Sim.

### **Potential Partners**

- B. Jacob (U. Maryland): Improve DRAM model

- S. Yalamanchili (Georgia Tech): Parallel SST

- D. Chiou (Texas): FPGA Acceleration of Simulation

## The modular simulation structure allows flexible simulation

Current and future SST user sites